1. 简介

Flip-chip(倒装芯片)封装广泛应用于桌面计算机、服务器和各种通讯设备。随着功能要求的提高,功率和热流密度越来越大。因此,对于高功率倒装芯片,客户在不断的推进TIM(热界面材料)的低热阻化。

TIMs(Thermal Interface Materials)是用于提高固体接触面之间传热性能的导热材料。比如CPUs和散热器之间,若出现微小间隙,由于空气导热性能极差,整个散热效率就会严重降低。因此,TIM的热特性对于散热方案的可靠性是至关重要的,尤其是发热部位的最高温度(结温Tj),散热片上表面温度(壳温Tc),和上述两点之间的热阻。测壳温Tc的传统方法是,在散热片中心放置一个热电偶。该方法的一个最大问题是只能用散热片中心位置的温度来表征壳温。但是在实际应用中,最高温度的位置我们通常不确定,尤其是当给结区加载非均匀热载荷(non-uniform power)的时候。

本文主要讨论的是:

a. 描述如何使用不借助热电偶的瞬态测试设备测试fcBGA封装器件(由STATS ChipPAC制造)的TIM热特性,尤其是结壳热阻Rjc;

b. 描述如何测试在风扇不同转速下(模拟真实工况)封装器件的Rja(结到环境的热阻);

c. 阐明功率脉普对结构函数的影响;

d. 描述如何通过仿真生成一个仿真结构函数,再用测试结构函数来修正仿真结构函数,最后用修正后的结构函数生成热阻网络模型,应用于系统级产品中;

e. 明确并改进更好的仿真和测试方法。

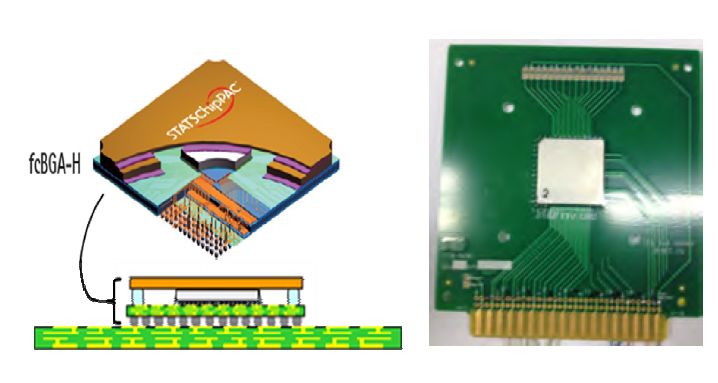

2. 封装器件和热测试装置的结构

STATS ChipPAC内部搭建了一个flip-chip测试装置(test vehicle),专门用于评估TIM的热特性,其结构如图1所示。待测封装器件包含如下结构,从上到下依次是:25x25x1 mm的铜制散热片,TIM层、硅芯片、底部填充层(a layer of underfill)以及焊接凸点(solder bumps)、12层总厚度为1.65mm的衬底、焊球、和PCB板。在四周,使用环氧树脂材料将铜盖和衬底粘合在一起。

图1测试装置图

图1测试装置图

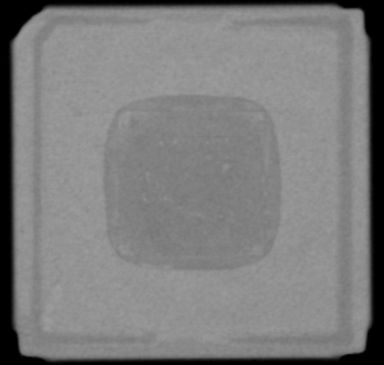

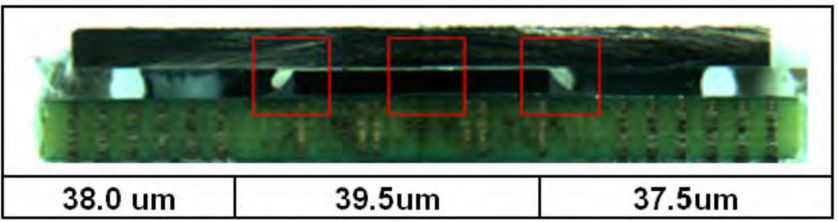

在结区涂TIM的时候,控制其范围要非常小心,且厚度被严格控制在38μm,误差不能超过2μm,如图2和图3所示。厚度通过在固化过程中涂了TIM之后,在散热片上部加载机械下压力来控制。

图2 TIM覆盖范围

图3 TIM厚度测量

图3 TIM厚度测量

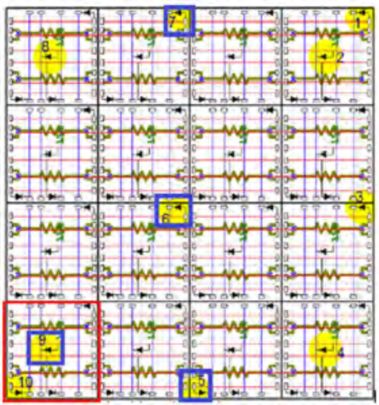

2.1 热测试芯片(Thermal Test Die)

现在Thermal test dies广泛应用于封装器件设计认证。图4展示了本次测试使用到的thermal test die,尺寸是10×10 mm。该芯片有4×4=16个单元,每个单元可以独立工作,也可以通过某些关联一起工作,比如均匀加热或非均匀加热。在芯片上分布有10个二极管传感器,可以用于测量中心位置、边上位置或者角落位置的温度。在本次测试中,所有16个单元都是均匀发热状态。

图4 Thermal test die

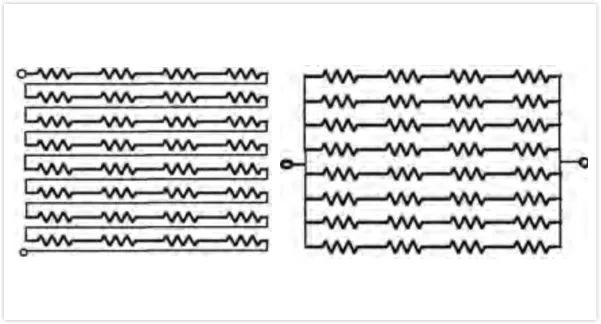

如图5所示,每一排的电阻器连接在一起,不同排之间的电阻器也联结在一起以保证同时加热整个结区,可以是并联或者串联的形式。区别在于串联能保证电阻器具有相同的电流,而并联则很难保证不同排电阻的电流强度,特别是当电流路径长度不同的时候。所以,还是采用串联比较好。

图5串联&并联加热电阻

2.2 二极管校准(标定k系数)

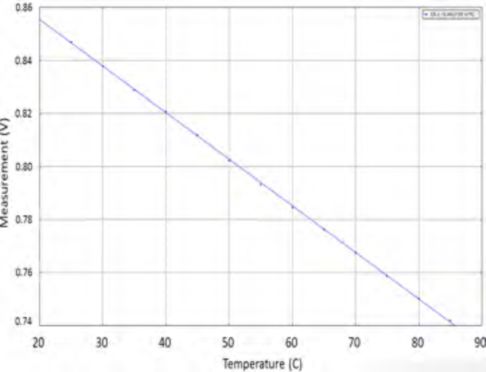

正如图4所示,10个二极管被置于硅芯片(silicon die)上,二极管用于测试该点的温度值。当给二极管通一小电流时,二极管两端的压降与温度呈线性关系。因此,在加热器件之前,需要先确定二极管压降和温度之间的函数关系,或称之为热敏参数。图6所示为标定该线性关系的实例。

图6 热敏感性(K系数) k = -1.755 mV/K

本次试验中,测试电流大约为5 mA,测试电压约为0.8 V,则一个二极管产生的焦耳热大约为4mW。假设结到环境的热阻为0.5 K/W,则该功率对升温的影响为

0.5 K/W x 4 mW = 0.002 ℃

可见该温升微乎其微,在大部分实际应用中均可忽略,这就保证了该测试方法的精度。

作者:Eric Ouyang, Billy Ahn, Robin Bornoff , Weikun He, Nokibul Islam,Gwang Kim, KyungOe Kim, Andras Vass-Varnai

2013 IEEE Semiconductor Thermal Management and Measurement Symposium

本文由上海坤道翻译整理,未经授权不得随意修改转载